[拼音]:erjiguan-jingtiguan luoji dianlu

[外文]:diode transistor logic

输入端用二极管实现“与”逻辑,输出端用晶体管实现“非”逻辑,采用二极管电平位移的单元门电路,简称DTL电路。其基本电路如图1。在图1a中的二极管D1、D2和D3完成“与”逻辑,二极管D4和D5提供补偿电压,晶体管T完成“非”逻辑,并提供增益。二极管D1、D2和D3的数目和“与”门输入端A、B、C的数目相同,增加二极管可扩展输入端数。

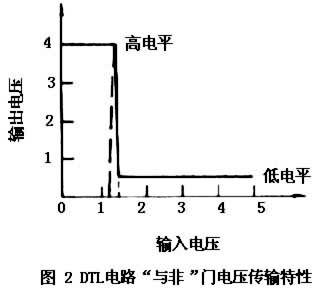

图2是 DTL电路的输入和输出电压传输特性。与直接耦合晶体管逻辑电路(DCTL)和电阻-晶体管逻辑电路(RTL)相比,DTL电路从“0”到“1”转换时的输入电压(阈值)比前者高。阈值升高是因为DTL电路增设了电平位移二极管D4和D5而得到的。阈值可由电平位移二极管的数目调整。一个硅二极管正偏压降约为0.7伏,当输入电压之一低于0.7伏时,其他输入端都接高电平或悬空,P点的电平低于1.4伏,这不足以使二极管D4和D5通导。经R1的电流全部从这一输入端流出,晶体管T处于截止状态,输出为高电平;当输入电压在0.7~1.4伏之间时,P点电平仍由输入电压和二极管正偏压降箝位。由于二极管D4和D5的电平位移作用,这时Q点电平仍在 0.7伏以下,晶体管T仍处于截止状态;只有当输入电压全都大于1.4伏后,P点电平由二极管D4和D5以及晶体管T的be结处于正偏通道,箝位在0.7×3=2.1伏,二极管D1、D2和D3均处于截止状态,经R1的电流全部从二极管D4和D5到晶体管基极输入端,使晶体管饱和,输出为低电平。输入电压为1.4伏左右时,对应于输出高、低电平的转折点,称为阈值电压。

DTL电路是一种饱和型电路,开关时间长,速度慢,是早期产品,在计算机的应用中已被其他形式的高速门电路所取代。但是,DTL电路具有线路简单和抗干扰性强等优点,常用于对速度要求不高的工业控制方面。

- 参考书目

- 复旦大学微电子教研组编:《集成电路设计原理》,人民教育出版社,北京,1978。沈铎编:《半导体数字集成电路》,国防工业出版社,北京,1980。